# **Design and Performance Analysis of Low Power ALU**

Dept. of E.C.E, NRI Institute of Technology, Pothavarapadu, Agiripalli, AP, India

# **Abstract**

In this paper, the gate level circuit of a 1-bit CMOS Arithmetic and Logic Unit (ALU) is designed and performance is analyzed. The main requirement of any technology is to design and develop low power circuit. Along with the power, high speed ICs are leading the VLSI industry. Here the performance of the proposed design is simulated and evaluated in terms of delay and power using tanner tools S-EDIT with different FANIN's using NAND gate. Power and delay has a major impact while designing any circuit. So, these factors play a major role in deciding the efficiency of the designed circuit.

## **Keywords**

CMOS, NAND, NOR, ALU, FANIN

### I. Introduction

Digital circuits consist of logic gates implemented in the Complementary Metal Oxide Semiconductor (CMOS) technology. The power consumption of these circuits has two components. The dynamic power is consumed only when the circuit performs a function and signals change. Leakage or static power is consumed all the time, i.e., even when the circuit is idle. The dynamic power cannot be eliminated completely because it is caused by the computing activity. It can, however, be reduced by circuit design techniques. Whenever a logic gate changes state, power is consumed. The solution is then realized at the transistor level designs. In this work, a 1-bit ALU is designed at transistor level for low power and minimum area. The rest of the paper is organized as follows; Section II will discuss about the ALU. Section III will discuss for the design of ALU cell. Followed by ALU designs, Simulation results and conclusion.

# II. ALU

In computing, an Arithmetic and Logic Unit (ALU) is a digital circuit that performs integer arithmetic and logical operations. The ALU is a basic block of the central processing unit of a computer, and even the simplest microprocessors that has a work of maintaining the timers. The processors accommodate very powerful and very complex ALUs inside modern CPUs and Graphics Processing Units (GPUs), a single component may contain a number of ALUs. Two important performance parameters of all digital circuits, for most applications are maximizing speed and minimizing power consumption. In this work, a 1-bit ALU is designed at transistor level for low power and minimum area. As per the analysis the power consumption is minimum with the channel length of 45 nm compared with the channel length of 90 nm.

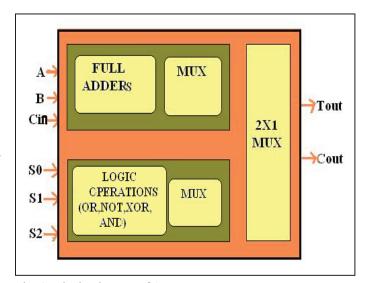

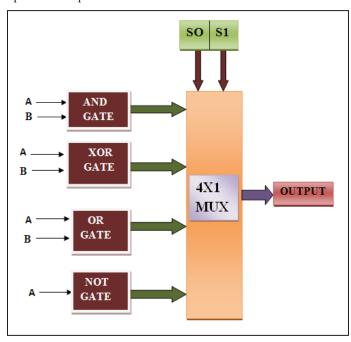

Fig. 1 shows the basic block diagram of ALU. These blocks are designed in such a way that all the arithmetic and logic operations are performed with accuracy in less area, delay and power. To decrease the size of this macro circuit, FAN-IN concept is used. A universal gate can implement any Boolean function without using any other gate. So, NAND gate realization of ALU is discussed here.

Fig. 1: Block Diagram of ALU

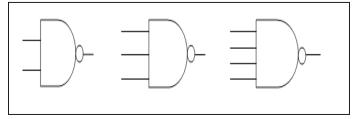

Fan-in is the number of inputs a logic gate can handle. Using logic gates with higher fan-in will help reducing the depth of a logic circuit. If number of input exceeds, the output will be undefined or incorrect. So we have restricted up to 4 inputs only. Fig. 2 shows NAND GATE with different FAN IN 2, 3 and 4.

Fig. 2: NAND GATE with FAN IN 2, 3 and 4.

# **III. Proposed Design**

# A. Design of a 1-bit ALU

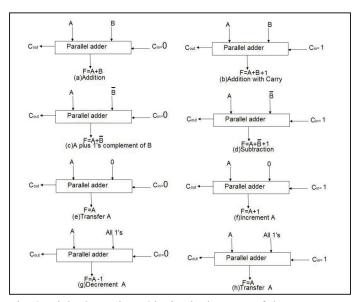

ALU which is a important element in central processing unit consists of arithmetic and logic units. These two basic units are comprised together using a summing unit. The main component for arithmetic unit is parallel adder, which consists of a number of full adders connected in cascade connection. The different types of operations can be obtained by this unit by changing the inputs to the parallel adder. Fig. 4 shows the arithmetic operations obtained when one of the two inputs is changed. Here A and B are two inputs of parallel adder, where B is changed and A remains the same.

The parallel adder inputs may be of any number of bits in value. The input carry C<sub>in</sub> given to the full adder circuit in the least significant bit position and the C<sub>out</sub> comes from the full adder circuit in the most significant bit position. From the fig. 3(a) to 3(h) various types of eight operations are achieved by changing the B input and C<sub>in</sub>. So to design the circuit we need two parts, one is control circuit and another one is full adder.

Fig. 3: Eight Operations Obtained when one of the Two Inputs is Changed

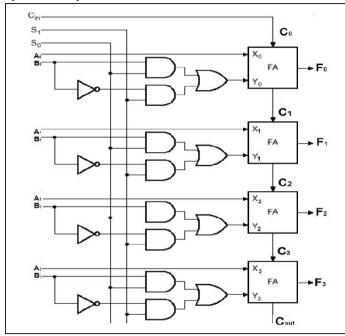

The basic logic diagram of a 4 bit arithmetic circuit is shown in fig. 4. This circuit controls the input B to provide various type of operation shown in fig. 4 and consists of two NAND gates, one OR gate and one NOT gate. S<sub>1</sub> and S<sub>2</sub> is two selection lines used to control the B input. When  $S_1 S_0 = 00$  the output of the OR gate Y=0, When  $S_1S_0 = 01$  the output of the OR gate Y=B, When  $S_1S_0 = 10$ the output of the OR gate Y=B', When  $S_1S_0=11$  the output of the OR gate Y=B+B'=1. This parallel adder constitutes of four full adders. The carry into the first stage is the input carry. The carry out of the fourth stage is the output carry. The selection variables are  $S_1$ ,  $S_0$  and  $C_{in}$ . Variables  $S_1S_0$  control all the B inputs to the full adder circuits. The A inputs go directly to the other inputs of the full adder section multiplexers plays an important role. A 4:1 Mux is used in the logic section. In the logic unit various operations like signed shifts (arithmetic left shift and the arithmetic right shift), logical shifts (logical left shift and the logical right shift), circular shift's (circular left shift and the circular right shift) etc., are performed. With the help of selection lines one of the logic operations is performed

Fig. 4: Logic Diagram of 4 Bit Arithmetic Circuit

The basic block diagram of a logic circuit is shown in fig. 5. For designing logic section multiplexers plays an important role. A 4:1 Mux is used in the logic section. In the logic unit various operations like signed shifts (arithmetic left shift and the arithmetic right shift), logical shifts (logical left shift and the logical right shift), circular shift s (circular left shift and the circular right shift) etc., are performed. With the help of selection lines one of the logic operations is performed.

Fig. 5: Block Diagram of a Logic Circuit

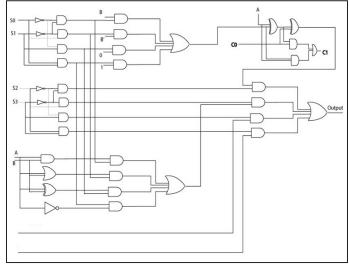

The gate level realization of the above discussed arithmetic and logic unit is shown in fig. 6. Using Boolean algebra the outputs are minimised and the total output equations for ALU are

Fig. 6: Gate Level Realisation of 1 Bit ALU CMOS Circuit

$$\begin{split} &T_{\text{out}} = (\text{A xnor } \text{C}_0) \text{ B'S}_0 \text{S}_2 \text{'} + (\text{A xor } \text{C}_0) \text{ B'S}_0 \text{'S}_2 \text{'} + (\text{A xnor } \text{C}_0) \text{ (B} \\ &\text{xor } \text{S}_0) \text{S}_1 \text{'S}_2 \text{'} + (\text{A xor } \text{C}_0) (\text{S}_0 \text{ xor } \text{S}_1) \text{BS}_2 \text{'} + \text{ABS}_1 \text{'S}_2 + \text{A'S}_0 \text{S}_1 \text{S}_2 \\ &+ (\text{A xor B}) \text{ S}_0 \text{S}_1 \text{'S}_2 + (\text{A xor B}) \text{ S}_0 \text{'S}_1 \text{S}_2 \\ &C_{\text{out}} = \text{S}_0 \text{'S}_1 \text{'B} (\text{A} + \text{C}_0) + \text{S}_0 \text{S}_1 \text{'A} \text{ (B'} + \text{C}_0) + \text{A'C}_0 \text{S}_0 (\text{S}_1 + \text{B'}) + \text{AS}_0 \text{'S}_1 \\ &C_0 + \text{AB'C}_0 \text{S}_0 \text{'} + \text{S}_0 \text{S}_1 \end{split}$$

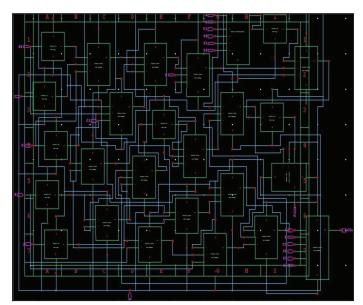

NAND realisation of the resulting circuit is designed completely using nand gates only. Further FAN-IN concept is implemented by increasing the inputs for respective NAND gates. These circuits

are designed in TANNER TOOLS S-EDIT. Power and delay calculations for the respective design is obtained

## **IV. Results**

# **A. Power Calculations**

Fig. 7: Simplified Gate Level Realization of 1 bit ALU

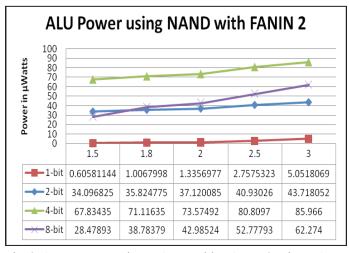

Fig. 8: ALU Power using NAND with FANIN 2 using NAND gate with FANIN 2

Fig. 9: Simplified Gate Level Realization of 1 bit ALU

www.iject.org

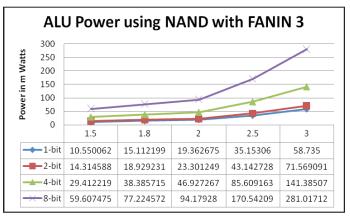

Fig. 10: ALU Power using NAND with FANIN 3 using NAND gate with FANIN 3

Fig 11: Simplified gate level realization of 1 bit ALU

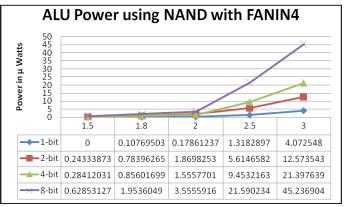

Fig. 12: ALU Power using NAND with FANIN 4 using NAND gate with FANIN 4

# **B.** Delay

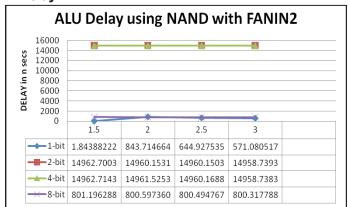

Fig. 13: ALU Delay using NAND with FANIN 2

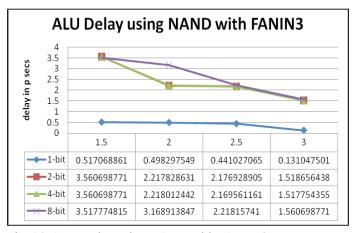

Fig. 14: ALU Delay using NAND with FANIN 3

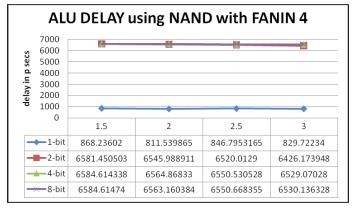

Fig. 15: ALU Delay using NAND with FANIN 4

# V. Conclusion

The circuit designed with NAND realization for 2input, 3input and 4input of 1-bit ALU are presented. Corresponding power calculation values are also presented. Comparing NAND power and delay values, we can observe that by increasing supply voltage the power will increase and delay will decrease. Going into depth we can observe that ALU with FANIN 3 has less delay compared to other designs. The power consumed is less for 1.8VDD when compared to that of 2.5 VDD. This is due to the reason that decrease in the VDD results in the reduction of overall power consumed. In this way comparing all the results the low power 1Bit ALU is obtained.

# References

- [1] Mr. Arindam Baul, Mrs. Akansha Awasthi, "Design and Implementation of Low Power ALU Design", International Journal Of Engineering And Computer Science, Vol. 6, Issue

- [2] N. Sabari Manoj, K. Suriya, "Design of Low Power 1 Bit ALU using CMOS", SSRG International Journal of VLSI & Signal Processing, Vol. 4, Issue 2, 2017.

- [3] Gauri Chopra, Sweta Snehi, "Design and Performance Analysis of High Speed Low Power 1 bit Full Adder", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 6, Issue 6, 2017.

- [4] Megha R, Vishwanath B R,"Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using CMOS Technologies Using Cadance", International Research Journal Of Engineering And Technology, Vol. 4, Issue 8, 2017.

- K.Rajasri, M.Manikandan, "High Speed Noise Tolerant Domino Circuit For Wide Fan-in AND-OR Gates", International Journal for Research in Applied Science & Engineering Technology, Vol. 3, Issue 5, 2015.

- Shefali Mamataj, Biswajit Das, Anurima Rahaman, "An Ease implementation of 4-bit Arithmetic Circuit for 8 Operation by using a new reversible COG gate", Vol. 3, Issue 1, 2014.

- [7] Advanced Computing, NOIDA, India. Review of Clock gating technique MIT International.

- [8] Journal of Electronics and Communication Engineering, Vol. 1, No. 2, pp. 106-114, 2011, MIT Publication.

- [9] Najm, F.N., "A survey of power estimation techniques in VLSI circuits", IEEE Transactions on very large scale integration (VLSI) Systems 2(4), pp. 446-455, 1994.

- [10] Tseng, Y.K., Wu, C.Y., "A 1.5 V Differential cross-coupled bootstrapped BICMOS logic for low voltage application", IEEE Journal of Solid-State Circuits 33(10), pp. 1576-1579,

- [11] Rabey, J.M., "Digital Integrated Circuits DA Design Perspective.

Ch.Swapna received her B.Tech degree in Electronics and Communications Engineering from Jawaharlal Technological University, Kakinada, Andhra Pradesh, India in 2011 and M.Tech degree in VLSI Design from Jawaharlal Technological University, Hyderabad, Telangana, in 2014. She is an assistant professor in the Department of Electronics and Communication Engineering at NRI Institute of technology from 2015 till

date. Her research interests include VLSI system design, image processing, speech processing, digital signal processing, embedded systems.