# **FPGA Implementation of Algorithmic Counter Based Wallace Multiplier**

# <sup>1</sup>Sanjeeva Rao B, <sup>2</sup>Ram Kumar A

<sup>1,2</sup>Dept. of ECE, Sir.C.R.R College of Engineering, Eluru, India

#### **Abstract**

In this paper presents an algorithmic approach to construct high speed Wallace tree multiplier using proposed 7:3 counter along with full adder and half adder. This power efficient and high speed method can be used to implement counter based Wallace multiplier suitable for FPGA or ASIC synthesis tools. This concept is less complex as it avoids conventionally used multiplication and addition steps. It is an optimized method for Very Large Scale Integration (VLSI), applications.

### **Keywords**

Wallace Multiplier, FPGA, ASIC, Counter Based Wallace, VLSI.

# I. Introduction

Multiplication is basic and most widely used operation in digital systems. wallace tree multiplication improves the speed of this multiplication process. The operation of the Wallace tree multiplier is divided in three steps as shown in the fig. 1.

Fig. 1: Block Diagram of Tree Based Multiplication

After generating partial products, half adders and full adders are used for reduction of these partial products, until those are reduced to two rows. These two rows are finally added in final adder in order to get the result of the multiplication. A large number of papers have been published in the literature to improve the performance of the Wallace multiplier. A Booth-encoded based Wallace multiplier is proposed in [3] which uses Booth encoding to generate the partial products. In [4], a layout strategy is proposed to reduce the wiring delay of the tree reduction. This approach results in a slightly faster multiplier as compared to the Wallace multiplier. A number of architectures use high speed counters in Wallace tree reduction to reduce the delay of the partial product tree reduction. The architecture in [6] uses a technique similar to Wallace reduction [2] to compute the sum of N inputs where all the inputs have the same weight. The architecture computes the 1s in the columns by using only the full adders. A modified form of this architecture is presented in [7] which uses Ripple Carry Adders (RCAs) and FAs to perform the counting. This paper proposes a structural approach which can be used to implement the counter

based Wallace multiplier. The proposed algorithm can be easily employed for the implementation of CBW multiplier of any size on FPGA and ASIC platforms.

The rest of the paper is organized as follows: Section II discusses the construction of the proposed Counter Based Wallace Multiplier (CBW). In Section III, simulation results of both traditional Wallace tree multiplier and proposed Counter Based Wallace Multiplier (CBW) are presented. The work is concluded in Section IV.

# II. Counter Based Wallace Multiplier (CBW)

In this proposed Counter Based Wallace Multiplier (CBW), we use only a 7:3 counter along with half adders and full adders. We used the 7:3 counter proposed in [10] due to its simple and fast circuit. The boolean equations used to implement this counter is given as follows:

### A. 7:3 Counter

The design of 7:3 counter is extensively studied in the literature and a number of architectures are proposed. The 7:3 counter proposed in [10] is selected for the proposed CBW multiplier due to its high speed operation. The Equation (1) gives the boolean functions for Sum, Cout1 and Cout2 for the 7:3 counter.

$$Sum = [(A \oplus B) \oplus (C \oplus D)] \oplus [(E \oplus F) \oplus G]$$

$$Cout1 = (w1 \oplus w2) \oplus w3$$

$$Cout2 = (w1.w2) + ((w1 \oplus w2).w3)$$

where

$$w1 = A.B + C.D + ((A + B).(C + D))$$

$w2 = [((E + F).G + E.F)]$

$w3 = [A.B.C.D + ((A \oplus B) (C \oplus D))].[(E \oplus F) \oplus G]$

The operation of counter based wallace multiplier is divided in three steps as shown in fig. 1.

For better understanding, this operation is simply explained using an 8-bit multiplication process.

# Step 1: Partial Product Generation

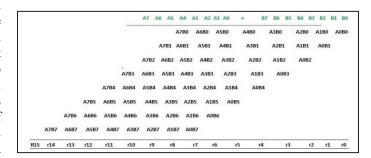

Let A and B are two 8 bit numbers.

A = [A7 A6 A5 A4 A3 A2 A1 A0]B = [ B7 B6 B5 B4 B3 B2 B1 B0 ]

The partial products for these two numbers as shown in following

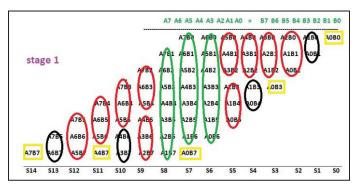

Fig. 2: Partial Product Generation and Reduction of Stage 1

# **Step 2: Reduction of Partial Products**

For reduction of partial products, in this approach, we use a 7:3 counter along with half adders and full adders. In stage 1, as shown in fig, combinations are made for reduction of computations, using a 7:3 counter along with half adders and full adders.

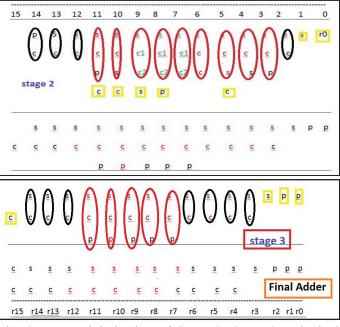

In stage 2, we have four rows, which are obtained from the reduction of the partial products of the eight rows.it is illustrated in fig. The reduction is from four rows to three rows, in stage 3. At this stage, these three rows are minimized to two rows using full adder and half adders.

# Step 3: Final Adder

Now, those two rows are added to obtain the final result. In this way, we can construct, any size of multiplication using this proposed algorithmic approach.

Fig. 3: Tree Minimization of Stage 2, Stage 3 and Final Addition

### **III. Simulation Results**

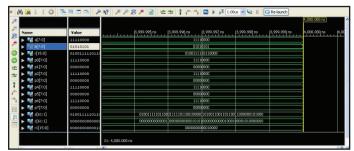

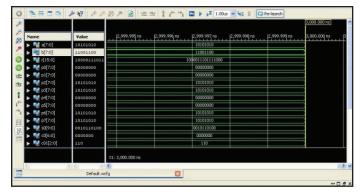

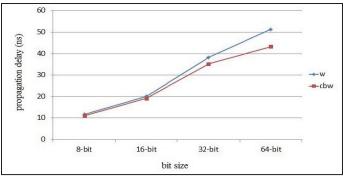

Both traditional Wallace and counter based Wallace multipliers are compared in this section. Simulation wave forms of traditional Wallace and counter based Wallace multipliers are separately illustrated in following, fig. 4 and fig. 5.

The internal computational stages are compared for 8-bit, 16-bit, 32-bit, 64-bit, 128-bit and 256-bit and summarized in Table 1'

Maximum combinational path delay: 11.719ns (5.517nslogic, 6.202ns route)(47.1% logic, 52.9% route) Maximum combinational path delay: 11.138ns. (5.274ns logic, 5.864ns route)47.4% logic, 52.6% route).

Fig. 4: Simulation Waveform for Wallace Multiplier

Fig. 5: Simulation Waveform for Counter Based Wallace Multiplier

For an 8-bit counter based Wallace multiplication, it is already shown in section II, that it require only three stages.

Both the multipliers are implemented using the XILINX version 10.1 and simulated using MODELSIM simulator.

Table 1: Comparison of Reduction Stages

| 1 &     |                                                          |                                                      |

|---------|----------------------------------------------------------|------------------------------------------------------|

| Size    | Number of stages of<br>traditional Wallace<br>multiplier | Number of stages of counter based Wallace multiplier |

| 8-bit   | 4                                                        | 3                                                    |

| 16-bit  | 6                                                        | 4                                                    |

| 32-bit  | 8                                                        | 4                                                    |

| 64-bit  | 10                                                       | 5                                                    |

| 128-bit | 11                                                       | 6                                                    |

| 256-bit | 13                                                       | 7                                                    |

Fig. 6: Comparision Graph

## **IV. Conclusion**

In this paper, power efficient and high speed counter based Wallace multiplication was discussed. This approach can be used to construct and implement any size of multiplication on FPGA as well as ASIC. In this approach we have used a 7:3 counter along with full adder and half adder. It is most suitable high speed applications. All the simulated waveforms are discussed.

### References

- [1] ShahzadAsif, Yinan Kong, "Design of an algorithmic Wallace multiplier using high speed counters", IEEE Transactions on Very Large Scale Integration (VLSI) Systems 2015.

- [2] C.S Wallace,"A suggestion for a fast multiplier", IEEE Electronic computers, Vol.EC-13, February 1964.

- [3] J. Fadavi-Ardekani, "M\*n booth encoded multiplier generator using optimized Wallace tree IEEE Transactions on Very Large Scale Integration (VLSI) Systems.

- [4] H. Eriksson, P. Larsson-Edefors, M. Sheeran, M. Sjalander, D. Johansson, M. Scholin, "Multiplier reduction tree with logarithmic logicdepth and regular connectivity," In Proc. IEEE Int. Symp. Circuits and Systems, 2006. ISCAS, Island of Kos, pp. 5–8, 2006.

- [5] R. S. Waters, E. E. Swartzlander, "A reduced complexity Wallace multiplier reduction," Transactions on Computers, Vol. 59, No. 8, pp. 1134–1137, 2010.

- [6] C. C. Foster, F. Stockton, "Counting responders in an associative memory," Computers IEEE Transactions on, Vol. C-20, No. 12, pp. 1580–1583, Dec 1971.

- [7] E. Swartzlander, "Parallelcounters," Computers, IEEE Transactions on, Vol. C-22, No. 11, pp. 1021–1024, 1973.

- [8] C. Vinoth, V. Bhaaskaran, B. Brindha, S. Sakthikumaran, V. Kavinilavu, B. Bhaskar, M. Kanagasabapathy, B. Sharath, "A novel low power and high speed wallace treemultiplier for risc processor," In Electronics Computer Technology (ICECT), 2011 3rd International Conference on, Vol. 1, 2011, pp. 330-334.

- [8] K. Prasad, K. Parhi, "Low-power 4-2 and 5-2 compressors", in Signals, Systems and Computers, 2001. Conference Record of the Thirty-Fifth Asilomar Conference on, Vol. 1, pp. 129–

- [9] C.-H. Chang, J. Gu, M. Zhang, "Ultra low-voltage lowpowercmos 4-2 and 5-2compressors for fast arithmetic circuits", Circuits and Systems I: Regular Papers, IEEE Transactions on, Vol. 51, No. 10, pp. 1985–1997, 2004.

- [10] M. Mehta, V. Parmar, E. Swartzlander, "High-speed multiplier design using multi-input counter and compressor circuits", In Computer Arithmetic, 1991. Proceedings. 10th IEEE Symposium on, Jun 1991, pp. 43-50.

- [11] L. Dadda, "Some schemes for parallel multipliers", Alta Frequenza, Vol. 34, pp. 349-356, 1965.

- [12] P. M. Kogge, H. S. Stone, "A parallel algorithm for the efficientsolution of a general class of recurrence equations," IEEE Transactions on Computers, Vol. C-22, No. 8, pp. 786-793, 1973.

- [13] J. Sklansky, "Conditional-sum addition logic", IRE Transactions on Electronic Computers, Vol. EC-9, No. 2, pp. 226-231, 1960.

- [14] R. P. Brent, H. T. Kung, "A regular layout for parallel adders," IEEE Transactions on Computers, Vol. C-31, No. 3, pp. 260-264, 1982.

- [15] T. Han, D. A. Carlson, "Fast area-efficient vlsi adders", in IEEE 8th Symposium on Computer Arithmetic, pp. 49–56, 1987.

- [16] S. Knowles, "A family of adders," In Proc. 15th IEEE Symposium on Computer Arithmetic, Adelaide, SA, pp.

- 277-281, 2001.

- [17] R. E. Ladner, M. J. Fischer, "Parallel prefix computation", Journal ofputing Machinery, Vol. 27, No. 4, pp. 831-838, 1980.

- [18] D. Harris, "A taxonomy of parallel prefix networks," In Conference Record of the Thirty-Seventh Asilomar Conference on Signals, Systems and Computers, Vol. 2, pp. 2213-2217, 2003.

- [19] V. Oklobdzija, D. Villeger, "Improving multiplier design by using improved columncompression tree and optimized final adder in cmos technology", Very Large ScaleIntegration (VLSI) Systems, IEEE Transactions on, Vol. 3, No. 2, pp. 292-301, 1995.

- [20] R. Ward, T. Molteno, "Table of linear feedback shift registers," Datasheet, Department of Physics, University of Otago,

- [21] S. Asif, Y. Kong, "Performance analysis of Wallace and radix-4 Booth-Wallace multipliers," In Electronic System Level Synthesis Conference (ESLsyn), pp. 17–22, 2015.

- [22] X.-V. Luu, T.-T.Hoang, T.-T.Bui, A.-V. Dinh-Duc, "A highspeed unsigned 32-bitmultiplier based on booth-encoder and wallace-tree modifications", In Advanced Technologies for Communications (ATC), 2014 International Conference on, Oct 2014, pp. 739-744.

- [23] M. Rao, S. Dubey, "A high speed and area efficient booth recoded wallace tree multiplier for fast arithmetic circuits", In Microelectronics and Electronics (PrimeAsia), 2012 Asia Pacific Conference on Postgraduate Research in, Dec 2012, pp. 220–223.inIntelligent and Advanced Systems (ICIAS), 2012 4th International Conference on, Vol. 2.

- [24] K. Swee, L. H. Hiung, "Performance comparison review of 32-bitmultiplier designs," In Intelligent and Advanced Systems (ICIAS), 20124th International Conference on, Vol. 2, pp. 836–841, 2012.

Sanjeeva Rao B received his B.Tech Degree in Electronics and Communications Engineering from Akula Gopayya College of Engineering and Technology, Tadepalligudem, India in 2012. At present, he pursuing M. Tech Degree in VLSI in Sir CRR College of Engineering, Eluru, India. His area of interests including low power VLSI design, Electronic measurement Techniques, Microcontrollers and Embedded Systems Design.

Ram Kumar A received his B.Tech degree in Electronics and Communications Engineering and M.Tech degree in VLSI systems design from Swarnandhra College of Engineering and Technology, Narsapur, India in 2007 and 2012 respectively. At present, he is an Assistant Professor in Dept. of ECE in Sir CRR college of engineering, Eluru, India. His research interests include digital signal processing and digital VLSI.